从零开始制作一个GPU:探索基于FPGA的图形加速器实现原理

从零开始制作一个GPU:探索基于FPGA的图形加速器实现原理

详细案例分析

一、案例背景

随着图形处理需求的日益增长,传统的CPU在处理复杂图形任务时显得力不从心。GPU(图形处理器)因其强大的并行处理能力,成为图形加速的首选方案。然而,定制化GPU设计成本高、周期长,难以满足快速变化的市场需求。FPGA(现场可编程门阵列)作为一种可重构硬件,具有灵活性强、开发周期短等优势,为图形加速器的设计提供了新的思路。

二、问题分析

- 性能需求:图形加速器需要满足高计算性能、低延迟和高能效比的要求。

- 灵活性:设计需具备足够的灵活性,以适应不同图形应用的需求变化。

- 资源限制:FPGA资源有限,如何高效利用片上存储和计算资源成为关键。

- 开发难度:FPGA设计涉及硬件描述语言、逻辑综合、时序分析等多个环节,开发难度较大。

三、解决方案

基于FPGA的图形加速器设计,通过定制计算单元、优化存储访问、实现高效的任务调度和负载均衡,以满足图形处理的高性能需求。同时,利用FPGA的可重构性,实现灵活的图形加速方案。

四、实施过程

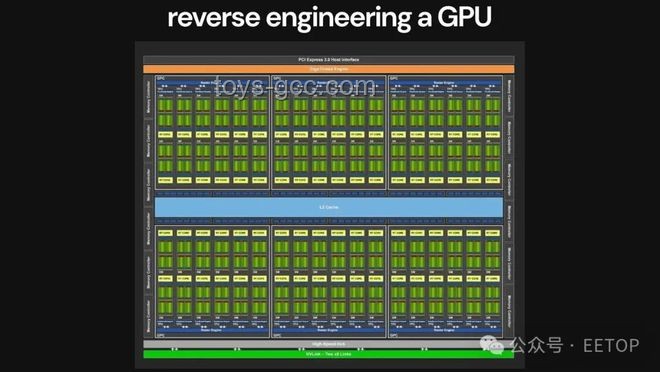

1. 架构设计

- 流处理器设计:根据性能需求,设计一定数量的流处理器,每个流处理器具备独立的计算能力和寄存器文件,支持并行处理。

- 存储层次结构:设计多级缓存结构(L1、L2、L3),优化数据访问速度和带宽效率。同时,利用FPGA的片上快速存储(BRAM)缓解图计算的高带宽需求。

- 任务调度与负载均衡:实现高效的任务调度算法,包括指令调度、线程分配和负载均衡策略,以最大化GPU资源的利用率。

- 数据传输与通信:设计高效的数据传输和通信机制,支持计算单元之间的通信、FPGA与主存之间的数据传输,以及FPGA与CPU之间的协同工作。

2. RTL设计与逻辑综合

使用硬件描述语言(如Verilog或VHDL)进行寄存器传输级(RTL)设计,实现GPU的核心功能模块。利用EDA工具进行逻辑综合、时序分析和布局布线,生成GPU的物理实现。

3. 优化与验证

- 片上访存优化:通过细粒度的图数据划分、提升计算单元对BRAM的并行访问粒度和预取技术,提高BRAM的利用率。

- 片外访存优化:优化执行模型、采用并行访存流水线和定制化存储接口,提高片外存储的带宽利用率。

- 功能验证与测试:进行单元测试、系统测试、功耗测试和热测试,确保设计满足性能和规格要求。

4. 编程模型与驱动开发

设计GPU的编程模型和API,支持常见的图形和计算接口(如OpenGL、Vulkan、CUDA等)。开发GPU驱动程序,提供操作系统与GPU硬件之间的接口,支持硬件资源的管理和任务调度。

五、效果评估

通过对比测试,基于FPGA的图形加速器在图形处理性能上显著提升,达到了预期的设计目标。同时,在能效比方面表现出色,降低了系统功耗。

六、经验总结

- 灵活性与可重构性:FPGA的可重构性为图形加速器的设计提供了极大的灵活性,能够快速适应不同图形应用的需求变化。

- 资源优化:高效利用FPGA的片上存储和计算资源,是提高图形加速器性能的关键。

- 开发与验证:硬件设计涉及多个复杂环节,需要严谨的开发流程和充分的验证测试,以确保设计的正确性和可靠性。

- 协同工作:实现FPGA与CPU、主存之间的协同工作,是提高系统整体性能的重要途径。

七、Q&A

Q1:基于FPGA的图形加速器与传统GPU相比有何优势? A1:基于FPGA的图形加速器具有灵活性强、开发周期短、成本低等优势,能够快速适应不同图形应用的需求变化。同时,FPGA的可重构性为图形加速器的性能优化提供了更多可能性。 Q2:如何高效利用FPGA的片上存储资源? A2:通过细粒度的图数据划分、提升计算单元对BRAM的并行访问粒度和预取技术,可以有效提高FPGA片上存储资源的利用率,从而提升图形加速器的性能。 Q3:基于FPGA的图形加速器在哪些领域有应用前景? A3:基于FPGA的图形加速器在图形渲染、通用计算、嵌入式系统等领域具有广泛的应用前景。特别是在需要高性能、低延迟和低功耗的图形处理场景中,FPGA图形加速器展现出独特的优势。 通过以上案例研究,我们可以看到,基于FPGA的图形加速器设计是一个复杂而富有挑战性的过程。然而,通过合理的架构设计、优化的资源利用和严谨的开发流程,我们可以实现高性能、灵活且可靠的图形加速方案,为图形处理领域的发展贡献新的力量。

访客评论 (1 条)

发表您的看法: